|

시장보고서

상품코드

1850222

자동 시험 장비 : 시장 점유율 분석, 산업 동향, 통계, 성장 예측(2025-2030년)Automated Test Equipment - Market Share Analysis, Industry Trends & Statistics, Growth Forecasts (2025 - 2030) |

||||||

Mordor Intelligence

Mordor Intelligence

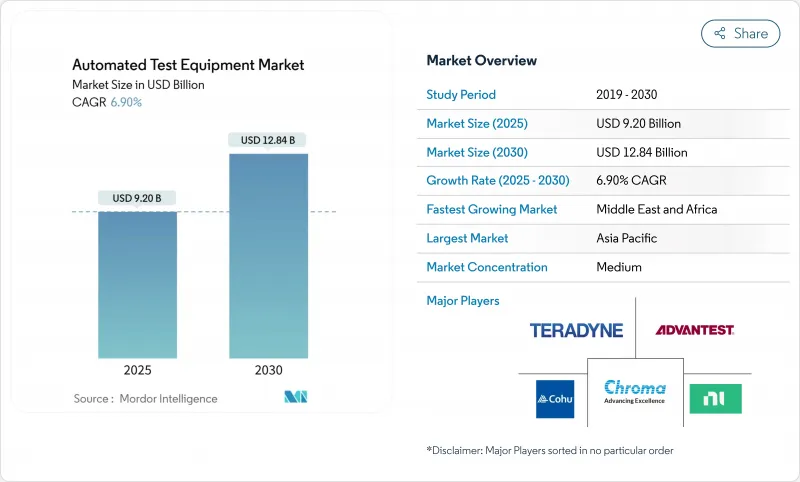

자동 시험 장비 시장 규모는 2025년에 92억 달러로 평가되었고, 2030년에는 128억 4,000만 달러에 이를것으로 예측되며, CAGR은 6.9%를 나타낼 전망입니다.

수요는 5nm 미만 공정으로의 전환, 차량의 전기화, 그리고 시스템 인 패키지(SiP) 설계의 복잡성 증가에 힘입어 가속화되고 있습니다. 제조사들은 10nV/√Hz 미만의 저잡음을 측정할 수 있는 초저잡음 플랫폼에 자본을 집중하고 있으며, 전력 장치 전문업체들은 1,200V 이상의 스트레스를 안전하게 적용할 수 있는 테스터를 요구하고 있습니다. 장비 공급업체들은 디버그 주기 단축과 수율 학습 향상을 위해 실시간 데이터 분석을 동시에 통합하고 있습니다. 주요 공급업체 간 통합은 지속되고 있으나, 혁신적인 중견 기업들은 AI 가속기용 웨이퍼 레벨 번인(burn-in) 및 광학 장치 신뢰성 검증과 같은 틈새 성장 분야를 목표로 삼고 있습니다.

세계의 자동 시험 장비 시장 동향 및 인사이트

초저잡음 ATE를 요구하는 7nm 미만 노드 축소

대만과 한국의 7nm 미만 생산 확대는 10nV/√Hz 미만의 측정 정밀도와 피코초 수준의 타이밍을 필수로 하고 있습니다. 주요 파운드리 업체들은 강화된 차폐와 최적화된 접지 참조를 통해 크로스톡을 억제하는 새로운 벡터 병렬 아키텍처를 인증함으로써 이에 대응하고 있습니다. 장비 공급업체들은 이러한 설계에 머신러닝 기반 패턴 생성을 결합하여 특성 분석 루프를 압축하고 있으며, 이 기능은 현재 플래그십 SoC 플랫폼의 표준 사양이 되었습니다.

자동차 기능 안전 IC 테스트 급증(ISO 26262)

유럽의 1차 반도체 공급업체들은 2024년부터 2025년 사이 결함 주입 기능이 있는 테스터의 도입을 34% 증가시켰습니다. 이 장비는 수백 가지 안전 목표 조합을 실행하며, 결과를 요구사항 추적성 매트릭스로 매핑합니다. 하드웨어 인 더 루프(HIL) 벤치와의 통합을 통해 파워트레인 인버터, 레이더 센서, MCU 서브시스템을 동시에 검증할 수 있어 대규모로 ASIL-D 준수를 보장합니다.

5nm 미만 테스터의 높은 자본 집약도와 긴 투자 회수 기간

플랫폼 가격이 7nm 세대 대비 35% 상승하면서 중견 파브의 투자 수익률(ROI)이 5년을 초과하게 되었습니다. 초안정 저유전율 절연체 프로빙, 고급 열 관리, 멀티테라비트 패턴 메모리 요구사항이 증가하면서 구매 및 서비스 비용이 상승해 중소 파운드리 업체의 도입 속도가 둔화되고 있습니다.

부문 분석

로직, SoC, RF 장치를 아우르는 비메모리 테스터는 2024년 자동화 테스트 장비 시장 점유율의 47.3%를 차지했습니다. 이들의 우위는 AI 프로세서, 5G 트랜시버, 자동차 도메인 컨트롤러 검수 수요에서 비롯되었습니다. 벤더들은 핀당 5Gbps를 초과하는 벡터 속도를 구현하고 혼합 워크로드를 지원하기 위해 서브테라헤르츠 RF 옵션을 추가했습니다. 머신러닝 기반 패턴 생성은 사이클 시간을 단축시켜 스마트폰 및 데이터센터 대량 생산에 적합했습니다. 통합 분석은 결함 시그니처를 레이아웃 블록과 연계하여 재설계 횟수를 줄이고 해당 부문의 매출 우위를 공고히 했습니다.

테스트 핸들러는 자동차 및 전력 라인이 더 높은 처리량과 엄격한 열 제어를 요구함에 따라 2025년부터 2030년까지 연평균 11.4% 성장률(CAGR)을 기록하며 가장 빠르게 성장하는 카테고리를 형성하고 있습니다. 핸들러용 자동 테스트 장비 시장 규모는 175°C에서 광대역갭 소자 검증을 위해 팹들이 다중 구역 플레이트와 능동 진동 감쇠를 요구함에 따라 확대되고 있습니다. 첨단 로봇 기술은 이제 미세 균열 없이 취약한 3D 적층 패키지를 이동시켜 SiP 조립의 1차 통과 수율을 높입니다. 예측 유지보수 소프트웨어는 가동 중단 시간을 추가로 단축하여 해당 부문의 두 자릿수 성장 궤도를 유지합니다.

테스터 메인프레임은 패턴 생성 가속기와 클라우드 연결 분석 모듈을 통합하는 업그레이드에 힘입어 2024년 매출의 56.4%를 차지했습니다. 인터페이스 보드는 이제 70Gbps 차동 레인을 지원하기 위해 저손실 라미네이트를 채택하고 있으며, 능동적 열 제어 소켓은 접합 온도를 ±0.5°C 이내로 안정화합니다.

시스템 레벨/번인 랙용 자동화 테스트 장비 시장 규모는 AI 가속기 웨이퍼 레벨 스트레스 테스트 및 포토닉스 어셈블리 검증 수요에 힘입어 연평균 12.9% 성장할 전망입니다. 프로버 혁신은 MEMS 스프링 프로브 카드를 통해 3μm 위치 정확도로 축소되는 패드 피치 문제를 해결합니다. 핸들러 설계는 안전이 중요한 자동차용 IC가 요구하는 확장된 온도 테스트 매트릭스에 대응하기 위해 다중 구역 쿨링 플레이트를 추가합니다.

자동 시험 장비 시장은 테스트 장치 유형별(메모리, 비메모리, 디스크리트, 테스트 핸들러), 컴포넌트별(테스터, 핸들러, 프로버, 기타), 테스트 단계별(웨이퍼 프로브 테스트, 기타), 기술 노드별(28Nm 이상, 14-22 Nm, 7-10Nm, 5Nm 이하), 최종 사용자 산업별(소비자 가전, 기타), 지역별(북미, 남미, 유럽, 아시아태평양, 중동 및 아프리카)으로 분류됩니다.

지역별 분석

아시아태평양 지역은 2024년 매출의 62.4%를 차지하며 자동화 테스트 장비 시장을 주도했습니다. 이는 대만, 한국, 중국 본토 및 일본에 밀집된 300mm 팹 클러스터에 힘입은 결과입니다. 3nm 및 2nm 노드에서의 파운드리 확장은 신주 및 경기도 전역에 걸쳐 초저잡음 최종 테스트 라인에 대한 투자를 촉발한 반면, 중국 IDM 업체들은 수출 제한을 상쇄하기 위해 국내 프로버 및 핸들러 조달을 가속화했습니다.

CHIPS 법안 인센티브로 애리조나, 텍사스, 뉴욕에 여러 그린필드 팹이 추진되면서 북미가 2위를 차지했으며, 주변 온도보다 40°C 낮은 스트레스 프로파일을 처리할 수 있는 패키지/최종 및 시스템 레벨 스테이션에 대한 새로운 수요가 발생했습니다. 멕시코의 자동차 전자 회랑 역시 인근 자동차 공장에 서비스를 제공하기 위해 핸들러 차량을 업그레이드했습니다.

유럽의 점유율은 기능 안전 IC 생산을 배경으로 증가했으며, 독일과 프랑스는 ADAS 프로세서 및 전력 모듈을 위한 테스트 용량을 확장했습니다. 한편, 430억 유로 규모의 유럽 칩스 법안은 2030년까지 지역 내 제조 생산량을 두 배로 늘리는 것을 목표로 하여, 테스터 주문도 동시에 촉진했습니다.

중동 및 아프리카 지역은 2025년부터 2030년까지 연평균 9.1% 성장률을 기록할 전망입니다. UAE와 사우디아라비아가 다각화 자금을 현지 RF 프론트엔드 벤처에 투자하고 있으며, 남아프리카공화국과 나이지리아의 아프리카 허브들은 지역 팹리스 스타트업들을 위한 혼합 신호 벤치 인증을 시작했습니다.

기타 혜택 :

- 엑셀 형식 시장 예측(ME) 시트

- 3개월간의 애널리스트 지원

목차

제1장 서론

- 조사의 전제조건과 시장의 정의

- 조사 범위

제2장 조사 방법

제3장 주요 요약

제4장 시장 상황

- 시장 개요

- 시장 성장 촉진요인

- 초저잡음 ATE를 요구하는 7nm 미만 노드 축소

- SiC/GaN 전력 소자가 고전압 개별 ATE 수요 주도

- 고전압 디스크리트 ATE를 주도하는 SiC/GaN 파워 디바이스

- 시스템-인-패키지(SiP) 성장으로 시스템 레벨 테스터 수요 증가

- 아시아 지역 5G/6G RF 프론트엔드 복잡성 증가

- 리쇼어링 인센티브(미국 CHIPS, EU 칩스 법안)로 테스트 역량 확대

- 시장 성장 억제요인

- 5nm 미만 테스터의 높은 자본 집약도와 긴 투자 회수 기간

- 온칩 BIST로 인한 외부 디지털 ATE 수요 감소

- 제한된 벤더 간 인터페이스 상호 운용성

- 주기적인 반도체 CAPEX 삭감

- 밸류체인 분석

- 규제/기술적 전망

- Porter's Five Forces

- 신규 참가업체의 위협

- 구매자의 협상력

- 공급기업의 협상력

- 대체품의 위협

- 경쟁 기업간 경쟁 관계

- 투자분석

- 거시경제 요인의 영향

제5장 시장 규모와 성장 예측

- 테스트 기기 유형별

- 메모리

- DRAM

- 플래시

- 비메모리

- 로직/SoC

- 믹스드 시그널과 아날로그

- RF

- 디스크리트

- 테스트 핸들러

- 메모리

- 컴포넌트별

- 테스터(코어 시스템)

- 핸들러

- 프로버

- 로드/인터페이스 보드 및 소켓

- 테스트 스테이지별

- 웨이퍼 프로브 테스트

- 패키지/최종 테스트

- 시스템 레벨/번인 테스트

- 기술 노드별

- 28nm 이상

- 14-22nm

- 7-10nm

- 5nm 이하

- 최종 사용자 업계별

- 소비자 가전

- IT 및 통신

- 자동차 및 EV

- 항공우주 및 방위

- 헬스케어 기기

- 산업 및 전력

- 지역별

- 북미

- 미국

- 캐나다

- 멕시코

- 남미

- 브라질

- 아르헨티나

- 기타 남미

- 유럽

- 독일

- 영국

- 프랑스

- 이탈리아

- 북유럽(스웨덴, 핀란드, 노르웨이, 덴마크)

- 기타 유럽

- 아시아태평양

- 중국

- 일본

- 한국

- 대만

- 기타 아시아태평양

- 중동 및 아프리카

- 중동

- 사우디아라비아

- 아랍에미리트(UAE)

- 튀르키예

- 기타 중동

- 아프리카

- 남아프리카

- 나이지리아

- 기타 아프리카

- 북미

제6장 경쟁 구도

- 시장 집중도

- 전략적 동향

- 시장 점유율 분석

- 기업 프로파일

- Advantest Corp.

- Cohu Inc.

- National Instruments(NI)

- FormFactor Inc.

- Hon Precision(Huafeng)

- TESEC Corp.

- Tokyo Electron(TEL)

- UniTest Inc.

- Shenzhen ChangHong Tech.

- Blue Chip Testers

- MAC Panel Company

- Star Technologies

- Samsung Semiconductor(Internal ATE)

- Teradyne Inc.

- Chroma ATE Inc.

- SPEA SpA

- Astronics Corp.

- InTest Corp.

- Toray Engineering

- Hangzhou ChangChuan Tech.

- Exicon Co.

- Leader Tech.

- Roos Instruments

- Virginia Panel Corp.

- Aeroflex Inc.(Cobham)

- Asset InterTech

제7장 시장 기회와 장래의 전망

HBR 25.11.19The Automated Test Equipment market size was valued at USD 9.20 billion in 2025 and is projected to climb to USD 12.84 billion by 2030, advancing at a 6.9% CAGR.

Demand is propelled by the migration to sub-5 nm nodes, the electrification of vehicles, and the rising complexity of System-in-Package designs. Manufacturers are channelling capital toward ultra-low-noise platforms able to measure below 10 nV/√Hz, while power-device specialists are specifying testers that safely apply in excess of 1,200 V stresses. Equipment vendors are simultaneously integrating real-time data analytics to shorten debug cycles and improve yield learning. Consolidation among leading suppliers continues, yet innovative mid-tier companies are targeting niche growth pockets such as wafer-level burn-in for AI accelerators and photonics device reliability validation.

Global Automated Test Equipment Market Trends and Insights

Shrinking <7 nm Nodes Requiring Ultra-Low-Noise ATE

Sub-7 nm production ramp-ups in Taiwan and South Korea have mandated measurement precision below 10 nV/√Hz and picosecond-level timing. Leading foundries have responded by qualifying new vector-parallel architectures that suppress crosstalk through enhanced shielding and optimized ground referencing. Tool suppliers are pairing these designs with machine-learning-driven pattern generation to compress characterization loops, a feature now standard on flagship SoC platforms.

Automotive Functional-Safety IC Testing Surge (ISO 26262)

European Tier-1 semiconductor vendors increased deployments of fault-injection-capable testers by 34% between 2024 and 2025. The equipment executes hundreds of safety-goal permutations, mapping results back to requirements-traceability matrices. Integration with hardware-in-the-loop benches enables simultaneous verification of powertrain inverters, radar sensors, and MCU subsystems, ensuring ASIL-D compliance at scale.

High Capital Intensity and Lengthy Pay-Back for Sub-5 nm Testers

Platform prices rose 35% versus the 7 nm generation, stretching ROI beyond five years for mid-tier fabs. The need for ultra-stable low-k dielectric probing, advanced thermal regulation, and multi-terabit pattern memory inflates both acquisition and service costs, tempering adoption rates among smaller foundries.

Other drivers and restraints analyzed in the detailed report include:

- SiC / GaN Power Devices Driving High-Voltage Discrete ATE

- Growth of System-in-Package Fuelling System-Level Testers

- On-Chip BIST Reducing External Digital ATE Demand

For complete list of drivers and restraints, kindly check the Table Of Contents.

Segment Analysis

Non-memory testers covering logic, SoC, and RF devices captured 47.3% of the Automated Test Equipment market share in 2024. Their dominance arose from demand to screen AI processors, 5G transceivers, and automotive domain controllers. Vendors lifted vector speeds beyond 5 Gbps per pin and added sub-terahertz RF options to serve mixed workloads. Machine-learning pattern generation trimmed cycle times, suiting smartphone and data-centre volume runs. Integrated analytics linked fail signatures to layout blocks, reducing respins and cementing the segment's revenue lead.

Test handlers form the fastest-growing category, with an 11.4% CAGR projected from 2025 to 2030 as automotive and power lines seek higher throughput and tighter thermal control. The Automated Test Equipment market size for handlers is widening as fabs specify multi-zone plates and active vibration damping to qualify wide-bandgap devices at 175 °C. Advanced robotics now moves fragile 3D-stacked packages without micro-cracking, raising first-pass yield in SiP assembly. Predictive-maintenance software further trims downtime, sustaining the segment's double-digit trajectory.

Tester mainframes held 56.4% revenue in 2024, bolstered by upgrades that integrate pattern-generation accelerators and cloud-connected analytics modules. Interface boards now employ low-loss laminates to support 70 Gbps differential lanes, while active thermal-control sockets stabilize junction temperatures within +-0.5 °C.

Automated Test Equipment market size for system-level/burn-in racks is projected to rise at 12.9% CAGR, driven by AI accelerator wafer-level stress testing and photonics assembly validation. Prober innovations address shrinking pad pitches through MEMS spring-probe cards offering 3 μm positional accuracy. Handler designs add multi-zone chill plates to match extended temperature test matrices demanded by safety-critical automotive ICs.

Automated Test Equipment Market is Segmented by Test Equipment Type (Memory, Non - Memory, Discrete, and Test Handlers), by Component (Tester, Handler, Prober, and More), by Test Stage (Wafer Probe Test, and More), by Technology Node (>=28 Nm, 14-22 Nm, 7-10 Nm, and <=5 Nm), End-User Industry (Consumer Electronics, and More), and Geography (North America, South America, Europe, Asia-Pacific, Middle East and Africa).

Geography Analysis

Asia Pacific led the automated test equipment market with 62.4% revenue in 2024, supported by dense clusters of 300 mm fabs in Taiwan, South Korea, mainland China, and Japan. Foundry expansions at 3 nm and 2 nm nodes triggered corresponding investments in ultra-low-noise final-test lines across Hsinchu and Gyeonggi provinces, while Chinese IDMs accelerated domestic prober and handler procurement to offset export restrictions.

North America ranked second as CHIPS Act incentives advanced multiple green-field fabs in Arizona, Texas, and New York, creating fresh demand for package/final and system-level stations capable of ambient-minus-40 °C stress profiles; Mexico's automotive electronics corridor likewise upgraded handler fleets to serve nearby vehicle plants.

Europe's share increased on the back of functional-safety IC production, with Germany and France expanding test capacity for ADAS processors and power modules, while the EUR 43 billion European Chips Act aimed to double regional fabrication output by 2030, spurring parallel tester orders.

The Middle East and Africa are projected to post a 9.1% CAGR from 2025 to 2030 as the UAE and Saudi Arabia channel diversification funds into local RF-front-end ventures; African hubs in South Africa and Nigeria have begun qualifying mixed-signal benches for regional fabless start-ups.

- Advantest Corp.

- Cohu Inc.

- National Instruments (NI)

- FormFactor Inc.

- Hon Precision (Huafeng)

- TESEC Corp.

- Tokyo Electron (TEL)

- UniTest Inc.

- Shenzhen ChangHong Tech.

- Blue Chip Testers

- MAC Panel Company

- Star Technologies

- Samsung Semiconductor ( Internal ATE)

- Teradyne Inc.

- Chroma ATE Inc.

- SPEA SpA

- Astronics Corp.

- InTest Corp.

- Toray Engineering

- Hangzhou ChangChuan Tech.

- Exicon Co.

- Leader Tech.

- Roos Instruments

- Virginia Panel Corp.

- Aeroflex Inc. (Cobham)

- Asset InterTech

Additional Benefits:

- The market estimate (ME) sheet in Excel format

- 3 months of analyst support

TABLE OF CONTENTS

1 INTRODUCTION

- 1.1 Study Assumptions and Market Definition

- 1.2 Scope of the Study

2 RESEARCH METHODOLOGY

3 EXECUTIVE SUMMARY

4 MARKET LANDSCAPE

- 4.1 Market Overview

- 4.2 Market Drivers

- 4.2.1 Shrinking <7 nm Nodes Requiring Ultra-Low Noise ATE

- 4.2.2 Automotive Functional-Safety IC Testing (ISO 26262) Surge in EU

- 4.2.3 SiC / GaN Power Devices Driving High-Voltage Discrete ATE

- 4.2.4 Growth of System-in-Package (SiP) Fuelling System-Level Testers

- 4.2.5 5G / 6G RF Front-End Complexity in Asia

- 4.2.6 Reshoring Incentives (US CHIPS, EU Chips Acts) Expanding Test Capacity

- 4.3 Market Restraints

- 4.3.1 High Capital Intensity and Lengthy Pay-back for Sub-5 nm Testers

- 4.3.2 On-Chip BIST Reducing External Digital ATE Demand

- 4.3.3 Limited Inter-Vendor Interface Interoperability

- 4.3.4 Cyclical Semiconductor CAPEX Cuts

- 4.4 Value Chain Analysis

- 4.5 Regulatory / Technological Outlook

- 4.6 Porter's Five Forces

- 4.6.1 Threat of New Entrants

- 4.6.2 Bargaining Power of Buyers

- 4.6.3 Bargaining Power of Suppliers

- 4.6.4 Threat of Substitutes

- 4.6.5 Competitive Rivalry

- 4.7 Investment Analysis

- 4.8 Impact of Macroeconomic factors

5 MARKET SIZE AND GROWTH FORECASTS (VALUE)

- 5.1 By Test Equipment Type

- 5.1.1 Memory

- 5.1.1.1 DRAM

- 5.1.1.2 Flash

- 5.1.2 Non-Memory

- 5.1.2.1 Logic / SoC

- 5.1.2.2 Mixed-Signal and Analog

- 5.1.2.3 RF

- 5.1.3 Discrete

- 5.1.4 Test Handlers

- 5.1.1 Memory

- 5.2 By Component

- 5.2.1 Tester (Core System)

- 5.2.2 Handler

- 5.2.3 Prober

- 5.2.4 Load/Interface Boards and Sockets

- 5.3 By Test Stage

- 5.3.1 Wafer Probe Test

- 5.3.2 Package / Final Test

- 5.3.3 System-Level / Burn-in Test

- 5.4 By Technology Node

- 5.4.1 >=28 nm

- 5.4.2 14-22 nm

- 5.4.3 7-10 nm

- 5.4.4 <=5 nm

- 5.5 By End-User Industry

- 5.5.1 Consumer Electronics

- 5.5.2 IT and Telecommunications

- 5.5.3 Automotive and EV

- 5.5.4 Aerospace and Defense

- 5.5.5 Healthcare Devices

- 5.5.6 Industrial and Power

- 5.6 By Geography

- 5.6.1 North America

- 5.6.1.1 United States

- 5.6.1.2 Canada

- 5.6.1.3 Mexico

- 5.6.2 South America

- 5.6.2.1 Brazil

- 5.6.2.2 Argentina

- 5.6.2.3 Rest of South America

- 5.6.3 Europe

- 5.6.3.1 Germany

- 5.6.3.2 United Kingdom

- 5.6.3.3 France

- 5.6.3.4 Italy

- 5.6.3.5 Nordics (Sweden, Finland, Norway, Denmark)

- 5.6.3.6 Rest of Europe

- 5.6.4 Asia-Pacific

- 5.6.4.1 China

- 5.6.4.2 Japan

- 5.6.4.3 South Korea

- 5.6.4.4 Taiwan

- 5.6.4.5 Rest of Asia-Pacific

- 5.6.5 Middle East and Africa

- 5.6.5.1 Middle East

- 5.6.5.1.1 Saudi Arabia

- 5.6.5.1.2 United Arab Emirates

- 5.6.5.1.3 Turkey

- 5.6.5.1.4 Rest of Middle East

- 5.6.5.2 Africa

- 5.6.5.2.1 South Africa

- 5.6.5.2.2 Nigeria

- 5.6.5.2.3 Rest of Africa

- 5.6.1 North America

6 COMPETITIVE LANDSCAPE

- 6.1 Market Concentration

- 6.2 Strategic Moves

- 6.3 Market Share Analysis

- 6.4 Company Profiles (includes Global level Overview, Market level overview, Core Segments, Financials as available, Strategic Information, Market Rank/Share for key companies, Products & Services, and Recent Developments)

- 6.4.1 Advantest Corp.

- 6.4.2 Cohu Inc.

- 6.4.3 National Instruments (NI)

- 6.4.4 FormFactor Inc.

- 6.4.5 Hon Precision (Huafeng)

- 6.4.6 TESEC Corp.

- 6.4.7 Tokyo Electron (TEL)

- 6.4.8 UniTest Inc.

- 6.4.9 Shenzhen ChangHong Tech.

- 6.4.10 Blue Chip Testers

- 6.4.11 MAC Panel Company

- 6.4.12 Star Technologies

- 6.4.13 Samsung Semiconductor ( Internal ATE)

- 6.4.14 Teradyne Inc.

- 6.4.15 Chroma ATE Inc.

- 6.4.16 SPEA SpA

- 6.4.17 Astronics Corp.

- 6.4.18 InTest Corp.

- 6.4.19 Toray Engineering

- 6.4.20 Hangzhou ChangChuan Tech.

- 6.4.21 Exicon Co.

- 6.4.22 Leader Tech.

- 6.4.23 Roos Instruments

- 6.4.24 Virginia Panel Corp.

- 6.4.25 Aeroflex Inc. (Cobham)

- 6.4.26 Asset InterTech

7 MARKET OPPORTUNITIES AND FUTURE OUTLOOK

- 7.1 White-space and Unmet-Need Assessment